## Switching Flow Graph Modelling of RRPP Based DC-DC Converter

### Divya Navamani<sup>\*</sup>, K. Vijayakumar A. Lavanya

EEE Department, SRM University; India, divyateddy1@gmail.com

### Abstract

**Objective:** Small-signal modelling is a widespread analysis practice in power electronic converters which is used to fairly accurate the performance of non-linear devices with linear equations. The order of the dc-dc depends on the non-linear elements of the system. As the number of non-linear element of the converter is high, it's modelling and control becomes extremely complicated. Thus, there is a need for generalization of such converters by small signal modelling. Traditional modelling schemes using the averaging and small-signal linearization procedures are utilised for the advance modelling of the converters. **Method:** In this work, the purpose of the switching flow graph (SFG) and the Mason's gain formula aid the solution of the equations. The duty cycle to output and the input to output transfer functions are obtained. Those transfer function can be used for closed loop examination. **Findings:** Open loop analysis of the converter is done and the outcomes are verified through simulation. Theoretical and simulation results are shown to prove the accuracy of the developed small signal models. The derived topology is unstable in open loop condition. A prototype is developed to validate the performance of the proposed topology. **Improvement:** Closed loop analysis can be carried out with any type of controller.

Keywords: Loops, Modelling, Stability, Transfer Function, Voltage Gain

### 1. Introduction

The dynamic behaviour of the dc-dc converter can be easily studied by modelling methods. Modelling techniques are introduced in dc converters to design the closed loop system and to read the stability issues of the system. In the last three decades, many modelling is presented and implemented. Most predominantly used modelling techniques are the state-space averaging method, Current injected equivalent circuit approach<sup>1,2</sup> Unified Topological modelling<sup>3</sup>, PWM switch modelling<sup>4</sup>, the Alternate form of PWM switch model<sup>5, 6</sup> and so on. In 2010, L.K. Wong used Mason's gain formula to model the Sepic converter<sup>7</sup>. The method is found to be simple to derive the transfer function of the converter.

There are several transfer functions to learn the dynamic model of the converter. This paper obtains the key transfer function such as input to output transfer function and duty cycle to output transfer function of the derived topology. These two transfer functions are used to design the compensation model of the converter. There are 5 state variables in the derived topology. In the case of State Space Averaging Approach (SSA), inversion of the 5X5 matrix is a tedious and time consuming. So, the signal flow graph modelling technique is a simple for high order system<sup>8</sup>. Isolated<sup>9, 15</sup> and non-isolated DC-DC converters are used in many applications such as renewable energy system<sup>10–13</sup>, Electric and Hybrid Vehicle<sup>14</sup> and so on.

This paper is constructed as follows: Section 2 initiates the proposed topology and its steady state analysis. Signal flow graph modelling and transfer function derivation is stated in section 3. Section 4 manifests the simulation and hardware results. Finally, the paper is summarized in section 5.

# 1.1 Steady state analysis of the proposed topology

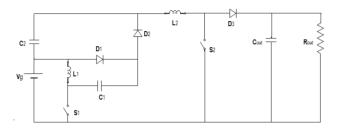

The topology is derived by Reduced Redundant Power Processing (RRPP) technique. A family of configuration is

offered for PFC regulator in<sup>8</sup>. In those 16 configurations, II-A configuration is chosen to derive a new topology with luo converter<sup>9</sup> and boost converter. Figure 1 gives the illustration of the suggested topology.

Figure 1. Proposed topology

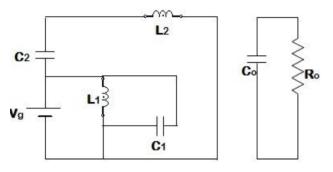

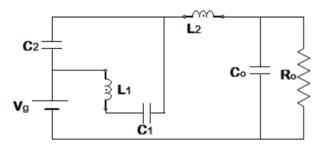

Figure 2. (a) Circuit under ON condition

(b) Circuit under OFF condition

Steady state analysis is carried out by volt-sec balance principle. Figure 2. (a) and (b) presents the circuit under on and off states respectively.

The state equations of ON state can be derived as follows

$$L_{1}\frac{d}{dt}\frac{d}{dt}i_{L1} = \mathcal{V}\mathcal{V}_{g} = \mathcal{V}\mathcal{V}_{C1}$$

(1)

$$L_{2}\frac{d}{dt}\frac{d}{dt}i_{L2} = v v_{g} + v v_{C2}$$

(2)

$$C_{1}\frac{d}{dt} v \frac{d}{dt} v = i_g - i_{L1} - i_{L2}$$

(3)

$$C_{2}\frac{d}{dt}v \frac{d}{dt}v _{C2}=i_{L2}$$

(4)

$$C_{0}\frac{d}{dt} v \frac{d}{dt} v c_{0} = -i_{0}$$

(5)

The state equations of OFF state can be derived as follows

$$L_{1} \frac{d}{dt} \frac{d}{dt} i_{L1} = v v_{C1} v v_{C2}$$

(6)

$$L_{2}\frac{d}{dt}\frac{d}{dt}i_{L2} = \nu \nu_{g} + \nu \nu_{C2} - \nu \nu_{C0}$$

(7)

$$-C_{1}\frac{d}{dt}\nu \frac{d}{dt}\nu_{C1} = -i_{g} + i_{L1} + i_{L2}$$

(8)

$$C_{2}\frac{d}{dt}v \frac{d}{dt}v _{C2}=i_{L2}-i_{L1}$$

(9)

$$C_{0}\frac{d}{dt}\nu \frac{d}{dt}\nu_{C0} = i_{L2} - i_{0}$$

(10)

### 1.2. Signal flow graph modelling

## 1.2.1 Perturbation and Small Signal linearization technique

The two inductors in the topology are averaged in on and off condition.

Inductor  $L_1$  is averaged in on and off condition, and the DC and AC equations are separated.

$$sL_{1} (\tilde{i}_{L1}+I_{L1}) = \tilde{v}_{c1}+V_{c1}-(1-D-d) d (\tilde{v}_{c2}+V_{c2})$$

(11)

DC equation:  $\overline{V}\overline{V}_{C1} = (1-\overline{D} \overline{D})(\overline{V} \overline{V}_{c2})$

AC equation:  $sL_{1}\tilde{i}_{L1} = \tilde{v}_{c1}-(1-\overline{D} \overline{D})\tilde{v}_{c2}+\tilde{d}\tilde{d}(V_{c2})$

Inductor  $L_1$  is averaged in on and off condition, and the DC and AC equations are separated.

$$sL_{2}(\tilde{i}_{12}+I_{12}) = \tilde{V}_{g}+V_{g}+\tilde{V}_{C2}+V_{C2}-(1-D-\vec{d})\vec{d} (\tilde{V}_{0}+V_{0})$$

(12)

DC equation:  $\vec{V}\vec{V}_{g}+\vec{V}\vec{V}_{C2}=(1-\vec{D}\vec{D})(\vec{V}\vec{V}_{0})$

AC equation:  $sL_{2}\tilde{i}_{12}=\tilde{V}_{g}+\tilde{V}_{C2}-(1-\vec{D}\vec{D})\tilde{V}_{0}+\vec{d}\vec{d}(V_{0})$

Capacitor  $C_1$  is averaged in on and off condition, and the DC and AC equations are separated.

$$sC_{1} (\tilde{\mathbf{V}}_{c1} + V_{c1}) = \tilde{\mathbf{i}}_{g}^{T} + I_{g} - (\tilde{\mathbf{i}}_{L1}^{T} + I_{L1}) - (\tilde{\mathbf{i}}_{L2}^{T} + I_{L2})$$

(13)

DC equation:

$$\overline{\mathbf{i}}_{g}^{T} = \overline{\mathbf{i}}_{L1}^{T} + \overline{\mathbf{i}}_{L2}^{T}$$

AC equation:

$$sC_{1} \tilde{\mathbf{V}}_{c1} = \tilde{\mathbf{i}}_{g}^{T} - \tilde{\mathbf{i}}_{L1}^{T} - \tilde{\mathbf{i}}_{L2}^{T}$$

Capacitor  $C_2$  is averaged in on and off condition, and the DC and AC equations are separated.

$sC_{2}(\tilde{\mathbf{v}}_{c2}+\mathbf{V}_{c2}) = (\tilde{\imath}\tilde{\imath}_{L2}+\mathbf{I}_{L2}) - (\tilde{\imath}\tilde{\imath}_{L1}+\mathbf{I}_{L1}) (1-D-d) d (14)$   $DC \text{ equation: } -\overline{II}_{0} + (1-\overline{D}\overline{D}) \overline{I} \overline{I}_{1,2} = 0$   $AC \text{ equation: } sC_{0}\tilde{\mathbf{v}}_{c0} = -\tilde{\imath}\tilde{\imath}_{0} + (1-\overline{D}\overline{D}) \tilde{D} \tilde{I} \tilde{\imath}_{L2} - \mathbf{I}_{L2}\tilde{d}\tilde{d}$

Capacitor  $C_0$  is averaged in on and off condition, and the DC and AC equations are separated.

$sC_{0} (\tilde{\mathbf{v}}_{c0} + \mathbf{V}_{c0}) = -\mathbf{\tilde{\iota}}_{0}^{T} - \mathbf{I}_{0} + (1 - \mathbf{D} - \mathbf{d} \mathbf{\tilde{J}} \mathbf{d} \mathbf{\tilde{J}} (\mathbf{\tilde{\iota}}_{L2}^{T} + \mathbf{I}_{L2})$ (15) DC equation:  $\mathbf{\overline{II}}_{L2} - \mathbf{\overline{II}}_{L1} (1 - \mathbf{\overline{D}} \mathbf{\overline{D}}) = 0$ AC equation:  $sC_{2} \mathbf{\tilde{v}}_{C2} = \mathbf{\tilde{\iota}}_{L2}^{T} - (1 - \mathbf{\overline{D}} \mathbf{\overline{D}}) \mathbf{\tilde{\iota}}_{L1}^{T} + \mathbf{I}_{L1} \mathbf{\tilde{d}} \mathbf{\tilde{d}}$

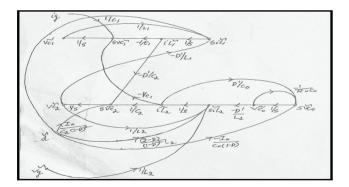

By taking the Laplace transform of the differential equations governing the system, AC equations can be derived. The constants and variables of s domain equations are identified as input, output, and intermediate variables. For every variable, a junction is designated in the graph. For each equation, a signal flow graph is sketched, and they are interconnected to provide overall signal flow diagram of the system. The AC equations written above are employed to develop a switching flow graph as shown in figure 3. All the independent states are characterized by the nodes, and the gain of the every path between the nodes can be received from the AC equations.

Figure 3. Signal flow graph of proposed topology

Table 1.Loops in signal flow graph

| Table 1. | Loops | in  | signal | flow   | graph  |

|----------|-------|-----|--------|--------|--------|

| Iubic I. | LOOPS | 111 | Signar | 110 11 | Siupii |

| Individual loops                                                                                                                                                                                                                                                                                 | Two non-<br>touching<br>loops                                                    | Three Non<br>Touching<br>Loops                                 |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| Loop 1: $\tilde{V}c_0 \rightarrow s\tilde{V}_{c_0} \rightarrow \tilde{V}_{c_0}$<br>L <sub>1</sub> = (-1/sR <sub>0</sub> C <sub>0</sub> )                                                                                                                                                         | $L_{1} \& L_{3} : (-1/s^{3}R_{0}C_{0}L_{2}C_{2})$                                | $L_{1}, L_{4}, L_{3}: (1/s^{5}R_{0}C_{0}L_{1}L_{2}C_{1}C_{2})$ |  |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                          | $L_1 \& L_4 : (1/s^3 R_0 C_0 L_1 C_1)$                                           |                                                                |  |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                          | $L_1 \& L_5 : (-D'^2/s^3R_0C_0L_1C_2)$                                           |                                                                |  |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                          | $L_1 \& L_6 : (-D'/s^5R_0C_0L_1L_2C_1C_2)$                                       |                                                                |  |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                          | $L_2 \& L_5 : (-D'^4)$<br>$s^4L_1L_2C_2C_0)$                                     |                                                                |  |  |  |

| Loop 6: $\tilde{i}_{L2} \rightarrow s \tilde{V}_{c1} \rightarrow \tilde{V}_{c1} \rightarrow$<br>$s \tilde{i}_{L1} \rightarrow \tilde{i}_{L1} \rightarrow s \tilde{V}_{c2} \rightarrow \tilde{V}_{c2} \rightarrow s \tilde{i}_{L2} \rightarrow \tilde{i}_{L2}$<br>$L_6 = (D'/s^4 L_1 C_1 L_2 C_2$ | $L_2 \& L_4 : (D'^2/s^4L_1C_1L_2C_0)$                                            |                                                                |  |  |  |

| $L_6 = (D / 3 L_1 C_1 L_2 C_2)$                                                                                                                                                                                                                                                                  | $\begin{array}{c} L_{3} \& L_{4}: (-1/\\ s^{4}L_{1}L_{2}C_{1}C_{2}) \end{array}$ |                                                                |  |  |  |

| Denominator $\Delta$ is,                                                                                                                                                                                                                                                                         |                                                                                  |                                                                |  |  |  |

| $\Delta = ((s^{5}R_{0}C_{0}L_{1}L_{2}C_{1}C_{2}) - [(-s^{4}L_{1}L_{2}C_{1}C_{2}) + (-s^{3}D^{2}L_{1}C_{1}C_{2}R_{0}) +$                                                                                                                                                                          |                                                                                  |                                                                |  |  |  |

| $(s^{3}L_{1}C_{1}R_{0}C_{0}) + (-s^{3}L_{2}C_{2}R_{0}C_{0}) + (s^{3}D^{2}L_{2}C_{1}R_{0}C_{0}) + (sD^{2}R_{0}C_{0})]$                                                                                                                                                                            |                                                                                  |                                                                |  |  |  |

| + {(- $s^2L_1C_1$ ) + ( $S^2L_2C_2$ ) + (- $s^2D'^2L_2C_1$ ) - 1 + D + (- $sC_1R_0D'^4$ ) +                                                                                                                                                                                                      |                                                                                  |                                                                |  |  |  |

| $(sD^{2}R_{0}C_{2}) + (-sR_{0}C_{0}) - (1)) /$                                                                                                                                                                                                                                                   |                                                                                  |                                                                |  |  |  |

| $(s^{5}R_{0}C_{0}L_{1}L_{2}C_{1}C_{2})$                                                                                                                                                                                                                                                          |                                                                                  |                                                                |  |  |  |

By analysing the graph in figure 3, there are 6 individual loops and 7 two non-touching loops and 1 three non-touching loops. Using Mason's gain formula, the denominator and numerator of the transfer function is obtained as shown in Table 1 and Table 2 respectively.

Table 2.

Numerator of the transfer function

| Parameter                                        | Vo/Vg                                                                 | Vo/d                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No of forward path                               | k = 1                                                                 | k = 4                                                                                                                                                                                                                                                                                    |

| Path gain                                        | $P_1 = D'/s^2 L_2 C_0$                                                | $P_{1} = -I_{O}/sC_{O}(1-D)$ $P_{2} = (2-D) D'/s^{2}C_{O}(1-D)$ $P_{3} = I_{O}D'/s^{3}C_{O}L_{2}C_{2}(1-D)^{2}$ $P_{4} = -VgD'2/s^{4}C_{O}L_{1}L_{2}C_{2}D'$                                                                                                                             |

| Loops not<br>touching the<br>for forward<br>path | $\ddot{A}_{1} = 1 - [(D^{2}/s^{2}L_{1}C_{2}) + (-1/s^{2}L_{1}C_{1})]$ | $\begin{split} &\Delta_1 = 1 - ((1/s^2 L_2 C_2) - (1/s^2 L_1 C_1) + (D^{2'}/s^2 L_1 C_2) + D'/s^4 L_1 L_2 C_1 C_2)) + ((1/s^2 L_2 C_2) - (1/s^2 L_1 C_1)) \\ &\Delta_2 = 1 - ((-1/s^2 L_1 C_1) + (D^{2'}/s^2 L_1 C_2)) \\ &\Delta_3 = 1 - (-1/s^2 L_1 C_1) \\ &\Delta_4 = 1 \end{split}$ |

#### 1.2.2. Designing of the converter:

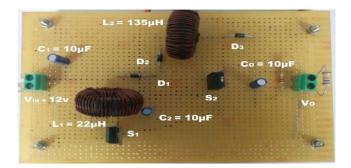

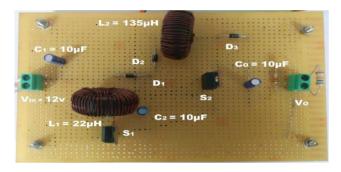

The converter is designed with the following circuit parameters for simulation and hardware: Vg = 10 V, R=130  $\Omega$ ; D = 0.3, Switching frequency (fs) = 60 kHz, Capacitors Co, C<sub>1</sub> and C<sub>2</sub> =10 $\mu$ F. Inductors are calculated with the derived equation (16) and (17).

$$L_1 = \frac{(1-D)^4 DR_L}{2(2-D)f_s}$$

(16)

$$L_2 = \frac{(1-D)^2 DR_L}{2f_s}$$

(17)

The Values of the inductors are  $L_1=22 \mu$ H,  $L_2=135 \mu$ H. By substituting the values input to output and control to output transfer functions are derived.

$$TF_{1} = \frac{\widetilde{V_{0}}}{\widetilde{V_{g}}} = \frac{0.369 \times 10^{9} \mathrm{S}^{3} + 1.225 \times 10^{18} \mathrm{S}}{\mathrm{s}^{5} + 769.2 \mathrm{S}^{4} + 2.7 \times 10^{9} \mathrm{S}^{3} + 2 \times 10^{12} \mathrm{s}^{2} - 0.81 \times 10^{18} \mathrm{S} - 3.7 \times 10^{21}}$$

(18)

$$S^{5} + 769.2 \mathrm{S}^{4} + 2.7 \times 10^{9} \mathrm{S}^{3} + 2 \times 10^{12} \mathrm{S}^{2} - 0.81 \times 10^{18} \mathrm{S} - 3.7 \times 10^{21}$$

Equation (18) and (19) gives the transfer function required for designing the compensation circuit.

### 1.3. Simulation and Hardware results

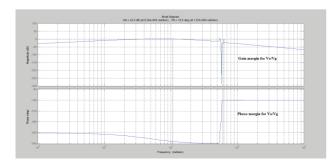

Stability analysis of the proposed topology is studied by obtaining bode plot and pole-zero map in MATLAB/ Simulink. Figure 4 (a)-(d) gives the Bode plot and polezero map of the transfer function. Matlab coding is recorded in m file, and it is simulated, and the results are offered in figure 4.

**Figure 4.** (a) Bode Plot for the transfer function Vo/Vg

(b) Poles and Zeros plot for the transfer function Vo/Vg

(c) Bode Plot for the transfer function Vo/d

(d) Poles and Zeros plot for the transfer function Vo/d

The steadiness of the converter can be measured by determining the poles and zeroes of the derived transfer function and sketching the Bode plot of the transfer function. From the Bode plot, gain and phase margin are noted. The gain margin input to output voltage transfer function is 24.4 dB and phase margin is 18.5 degree. The gain margin and phase margin of control to output voltage transfer function are -53.2 dB and -85.5 degree respectively. If the phase margin is low and negative, the system is unstable. There is one zero in the right half of the S- plane in both the transfer function. These two conditions conclude that the system is unstable. The compensating circuit can be derived with the help of these transfer function.

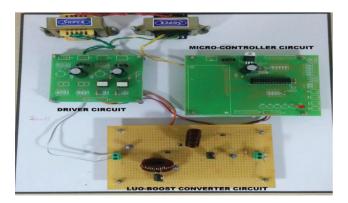

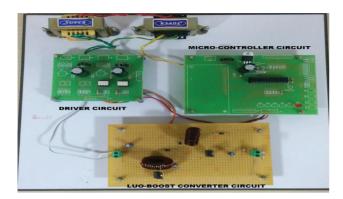

Figure 5. (a) Photograph of complete circuit

(b) Photograph of Proposed topology

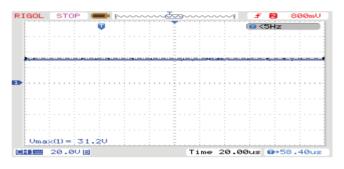

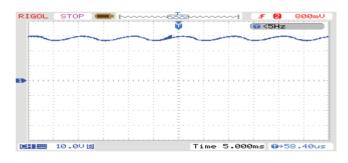

(c) Output voltage

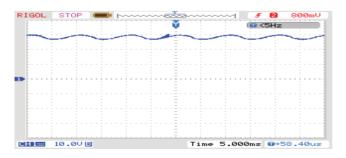

(d) Output capacitor voltage

A prototype is developed to validate the effectiveness of the converter. The output voltage is measured for D=0.3, and it is found to 31 V as shown in figure 5(c). Due to

the parasitic components, hardware results are less than the calculated results. Conventional boost converter with the same circuit parameters provides an output of 14 V. With the derived topology, voltage gain of the converter is increased. Figure 5(a) and (b) gives the photograph of the derived converter. Figure 5(d) shows the voltage across the output capacitor.

## 2. Conclusion

The proposed converter gives a high voltage boost even for low power input. Research indicates that these can even be used in applications where the variable load is needed. Transfer functions of the proposed DC-DC converters are obtained by the mason's gain formula and it is presented in this work. Averaging and small signal linearization techniques have been applied, and the measures of deriving transfer functions from the core state equations have been presented. The utilize of the signal flow graph and the Mason's gain formula helps to solve composite high order symbolic equations step by step. This allows us to handle many state variables in a convenient way. The duty cycle to output and the input to output transfer functions have been derived. The converter circuit is designed, simulated in MATLAB and the bode-plot has been found out to read the stability of the system. The boosting of the voltage of the derived topology has been implemented and validated using hardware.

### 3. References

- 1. Chetty P.R.K. Current Injected Equivalent Circuit Approach to Modelling Switching DC-DC Converters, IEEE Transactions on Aerospace and Electronic Systems, 1981; Nov : 17(6), 802–8.

- 2. Chetty P.R.K.. Current Injected Equivalent Circuit Approach to Modelling Switching DC-DC Converters in discontinuous inductor conduction mode, IEEE Transactions on industrial electronics, 1982: Aug; 29(3), 230–34.

- AndrzejPietkiewicz, Daniel Tollik. Unified Topological Modeling Method Of Switching Dc-Dc Converters In Duty-Ratio Programmed Mode, IEEE Transactions On Power Electronics, 1987; July: 2(3), 218–26.

- Edwin van Dijk, Herman J. N. Spruijt, Dermot M. O'Sullivan, J. Ben Klaassens. PWM-Switch modeling of DC-DC Converters, IEEE Transactions on Power electronics,1995; Nov:10(6),659–65.

- Ngo.K.,D.T, Alternate form of the PWM switch model. IEEE Transactions on Aerospace and Electronic system. 1999; Oct : 35(4),1283–92.

- 6. Chen, J. K.D.T. **Alternate forms** of the **PWM switch** model in discontinuous conduction mode, IEEE Transactions on Aerospace and Electronic Systems, 2001; Apr: 37(2), 754–58.

- Wong L.K, Man T.K. Small signal modelling of open-loop SEPIC converters, IET Power Electron., 2010; Nov: 3(6), 858-68.

- 8. Chi K. Tse, Martin H. L. Chow, Martin K. H. Cheung, A Family of PFC Voltage Regulator Configurations with Reduced Redundant Power Processing, IEEE Transactions On Power Electronics, 2001; NOV: 16(6), 794–802.

- 9. Divya Navamani Jayachandran, Vijayakumar Krishnaswamy, Lavanya Anbazhagan,etal., **Modelling and Analysis of Voltage Mode Controlled Luo Converter**, *American Journal of Applied Sciences*, 2015: Nov; 12(10), 766–74.

- Saravanan T, Srinivasan V, Sandiya P .A Two Stage DC-DC Converter with Isolation for Renewable Energy Applications, Indian Journal of Science and Technology, 2013; June: 6(S6), DOI no:10.17485/ 2013/v6i6/33970.

- Kavya Santhoshi B., Mohana Sundaram K., Sivasubramanian M., Akila S.A Novel Multiport Bidirectional Dual Active Bridge Dc-dc Converter for Renewable Power Generation

Systems, Indian Journal of Science and Technology, 2016; Jan: 9(1), DOI no:10.17485/ Indian Journal of Science and Technology /2016/v9i1/85701.

- Mahalakshmi R., Sindhu K. C, Thampatty. Implementation of Grid Connected PV array using Quadratic DC-DC Converter and Single Phase Multi Level Inverter, Indian Journal of Science and Technology, 2015; Dec:8(35), DOI no:10.17485/ Indian Journal of Science and Technology /2015/v8i35/80548.

- Jayaprakash, Ramakrishnan V. A New Single-stage Solar Based Controlled Full-bridge DC-DC Converter, Indian Journal of Science and Technology, 2014; Jan:7(9), DOI no:10.17485/ Indian Journal of Science and Technology /2014/v7i9/51106.

- Kirill Sidorov, Timofey Golubchik, Vladimir Yutt,Method for Calculating the Power Circuit Characteristics of the Isolated DC-DC Converters for Electric and Hybrid Vehicles, Indian Journal of Science and Technology, 2015; Oct: 8(27), DOI no:10.17485/Indian Journal of Science and Technology/v8i27/81709.

- Divya Navamani J, Vijayakumar K and Lavanya A." FPGA-based Digitally Controlled Isolated Full-Bridge DC-DC Converter with Voltage Doubler (IFBVD)", Indian Journal of Science and Technology, 2016; April: 9(16), DOI: 10.17485/Indian Journal of Science and Technology/2016/ v9i16/76672.